一、中芯国际高管变动,从梁孟松到蒋尚义2021年11月11日,全国可能海外都疯狂双十一,中芯国际高管又一次迎来人事变动,其副董事长、执行董事蒋尚义以希望更多时间陪伴家人为由提出辞呈,这距离蒋博士就职还不到一年。纵观蒋尚义履历,纵身半导体行业超过40年,曾在德州仪器、惠普工作,后出任台积电研发副总裁。2013年底,蒋尚义出任台积电共同运营长;2016年底出任中芯国际独立非执行董事;后转战武汉弘芯(ESMC-国际电子商情,2021)。

同时,梁孟松辞去执行董事一职,保留联合首席执行官职位。梁孟松,于台湾国立成功大学的电机工程系获得学士、硕士学位,后于加州大学伯克利分校拿到电机博士学位。毕业后进入AMD工作。1992年加入台积电,2009年离职,进入韩国大学教书。2011年进入三星,担任研发副总,工作了2年。2013年加入中芯国际(腾讯网-企鹅号1, 2021)。

[pic: 左-梁孟松,右-蒋尚义]

本次中芯国际人事变动,也有媒体认为是线路争议。先说说前缘,蒋尚义与梁孟松曾于台积电共同作战十余年,两人在2003年攻克130nm铜制程技术立下不小的功劳。技术侧重点上,蒋尚义在先进封装有丰富的经验,而梁孟松一直致力于先进制程,曾带领中芯国际从28nm向14nm迈进。如今,中芯国际在试产7nm(腾讯网-企鹅号2,2021)。值得一提的是,梁孟松系胡正明弟子。

1998年,加州大学伯克利分校胡正明教授在美国国防部高级研究项目局(Defense Advanced Research Projects Agency, DARPA)资助下,带领自己的技术团队,对CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)晶体管工艺技术的拓展进行研究,研究目的,如何将晶体管密度制程,提高到25nm。

胡正明教授在三维结构的MOS晶体管基础上,进一步提出了自对准的双栅MOSFET结构(Double gate structure Metal-Oxide-Semiconductor Field-Effect Transistor, 双栅金氧半场效晶体管)。

随后,胡正明教授及其团队成员发表了有关FinFET晶体管(Fin Field-Effect Transistor,鳍式场效应晶体管,1999年发布)和UTB-SOI技术(Ultra Thin body and BOX-Fully Depleted-silicon on insulator, UTBB-FD-SOI,超薄基体埋氧全耗尽绝缘层基硅,2000年发布),并于当年制造出来基于该技术的晶体管,栅长度仅为17nm,沟道宽度20nm,鳍(Fin)高度50nm,为全球第一个25nm以内的晶体管(知乎问答,2020)。

[pic: 胡正明博士,

点击获取来源]

二、中芯国际与台积电对比看行业发展

中芯国际(SMIC)在行业内属于什么水平?

2000年,中芯国际总部在上海成立,2004年于纳斯达克上市。晶圆厂主要在大陆,于美国、欧洲、日本、台湾地区设立办事处,于香港设立代表处。从产能角度而言,中芯国际排第五,市场份额3.6%,80%产能为成熟工艺。2020年,中芯国际在6家承销商的努力下,于上交所创业板上市,不同会计准则分开考察,趋势合并分析。招股说明书中,中芯国际披露其于全球纯晶圆代工市场份额约为6%。

一家行业第五名的、纯晶圆代工厂为主营的上市公司的高管人事变动能够给行业什么启示?首先,从技术上看,半导体领域的目标,简言之即减小体积并保证功能合适。这一目标使得晶体管从平面发展到鳍式,再到环绕栅,最后在环绕栅宽度与工艺上有所创新。其次,擅长封装的蒋尚义与擅长制程的梁孟松在发展方向上产生分歧,这会是其他参与者的困扰吗?

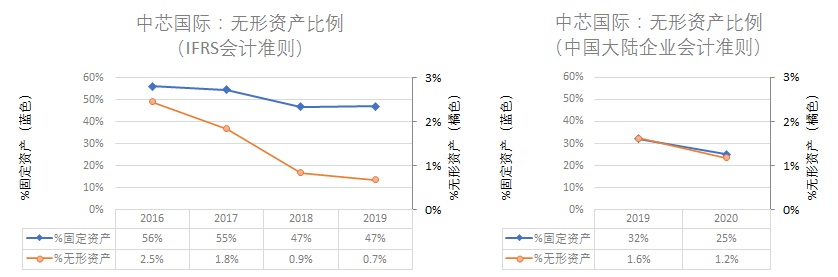

从财务基本面观测,中芯国际2019年收入缩水一半,2020年略微回升,不排除2020年中芯国际上市造成的影响,成本比例基本没改变。由于中芯国际的固定资产比例和无形资产比例几乎没改变,笔者认为该公司应该更致力于销售,通过增加订单和份额的方式增加收入。

[pic: Revenue Trend on SMIC]

[pic: 无形资产、固定资产比例,显示中芯国际致力于销售,扩大市场份额]

再观台积电,台积电高管相对比较低调,其CEO魏家哲于耶鲁大学获得电机工程博士学位,兼职台湾半导体行业协会主席。先后于新加坡特许半导体制造有限公司、德州意法半导体公司、台积电任职(与非网,2017)。

魏哲家说,这个行业靠的是创新、合作,更是努力。他还谈到,台积电的三个主要支撑点:技术、生产以及客户对台积电的信任,客户永远拥有台积电最好的的支持,台积电永远不会和客户们竞争。在任期间,魏家哲带领台积电成为世界上第一家能量产7nm支撑的半导体公司,提出 “Zero Excursion Zero Defect” 的品质目标(知乎-智东西,2019)。

[pic: TSMC目标]

2020年6月,台积电确认消息称,计划斥资120亿美元扩建芯片代工厂,这部分资金来自于同年3月的债券发行所募集的资金。与此同时,台积电还在争取美国参议院540亿美元的补贴。

产品创新方面,台积电已经研发出5nm制造工艺,用于汽车制造、人工智能等高端应用。但这部分产能不会影响芯片短缺,由于此次“缺芯潮”主要是欠缺依赖8寸晶圆的基础芯片产能。未来产能投资计划,台积电计划2020年至2023年计划投资1000亿美元(网易科技,2021)。

台积电近几年致力于制程工艺,2020年宣称将获得2023年苹果3nm芯片代工的权利,在芯片代工领域,形成与客户企业(例如,苹果、英特尔)和睦相处的模式。2021年12月,媒体报道Intel将派高管前往台积电,以达成合作关系。据悉,台积电3nm量产产能主要供应苹果,而Intel旗下的14代酷睿芯也需要3nm芯片做支撑(腾讯网-世界经理人商业,2021)。

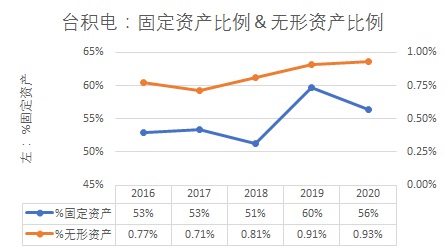

无论是新闻还是财务面,台积电都显示出和中芯国际所不同的企业经营理念。首先,2019年台积电的收入和利润率都受到一定影响,但下降较为有限。2020年,毛利率和净利率双双回升,甚至超过下降之前状态,达到近5年来毛利率和净利率的最高峰,分别为53%和38%。

[pic: 台积电毛利率、净利润率趋势]

另一方面,固定资产占总资产比例持续走高,印证了媒体宣称的台积电不断扩大工厂产能的描述。无形资产比例常年低于1%,这与台积电较高收入的绝对值有关。即便如此,该公司无形资产比例也持续增加,可见其公众形象与内部组织行为的一致性。

[pic: 台积电固定资产、无形资产占总资产比例]

三、芯片技术发展看门道

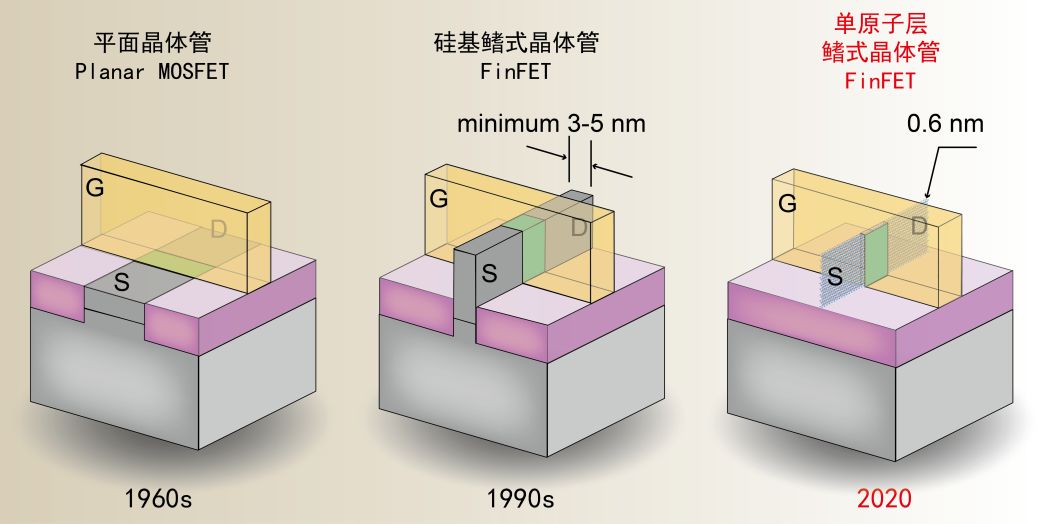

[pic: History of Field Effect Transistor 晶体管发展历史]

平面晶体管(Planar Field Effect Transistor, Planar FET),是60年代发展起来的一种非常最重要的半导体技术,使用该工艺所制作出的晶体管均称作平面晶体管。这种晶体管的基区一般用杂质扩散技术制作,由于杂志浓度不均匀,即表面高、内部低,因此可产生漂移电场,对注入到基区的少数载流子有加速运动的作用,性能优于均匀基区晶体管。

随着芯片尺寸减小,平面晶体管出现了短沟道效应(Short-Channel Effect),即由于制程(Gate Length)过小而产生问题,造成功率损耗,其中漏电现象最为严重。为了在短制程之间也能让电子较好地通过,晶体管开始向三维发展,即鳍式晶体管FinFET。其要义是使得源极到漏极的沟道(Channel)竖立着穿过Gate,一如鱼鳍(搜狐号-风尘孤狼,2019; 知乎-张竞扬,2020)。

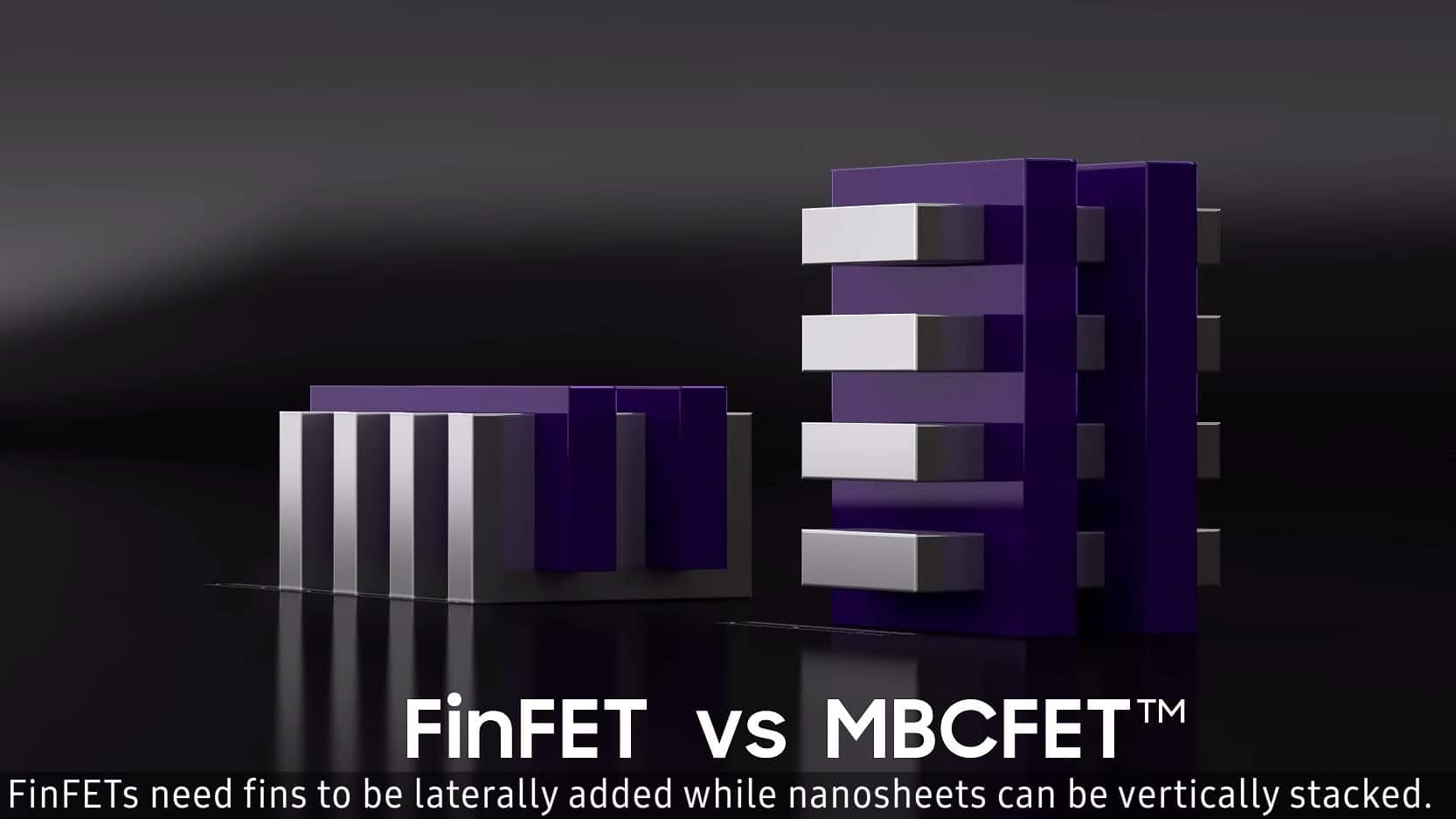

FinFET在业界使用许久,10nm以下制程几乎只能采用FinFET结构,但是短沟道效应仍然存在,人们仍然以摩尔定律的速度,追赶制程减少的进度。为了改善这一情况,提出了环绕栅晶体管,即GAAFET,Gate-All-Around FET。GAAFET包揽了5nm制程以下的产品,这种晶体管技术增加了沟道数量,使其内嵌于Gate中,以使得Gate对沟道的控制能力加强(知乎-石大小生,2021)。

[pic: 纵轴电压,横轴电流。GAA电流较低,功耗较少]

几乎和GAAFET同一时期提出的解决方案是多桥通道晶体管,即MBCFET(Multi-Bridge Channel FET)。MBCFET为三星研制并申请专利,结合FinFET与GAAFET的设计初衷,加宽了环绕栅之间的沟道,是短沟道效应的最新解决方案。

[pic: FinFET v.s. MBCFET]

目前,GAAFET和MBCFET都向2nm制程前进。台积电3nm量产技术,据悉已获得苹果大部分订单,而三星也在2021年10月,官方宣称已经实现3nm制程量产(海西商界,2021;知乎-科技美学,2021)。2020年台湾国际半导体展(SEMICON TAIWAN),台积电对媒体释放消息,称已经突破2nm大关,采用的是MBCFET结构,预计2024年量产(电子工程专辑,2020; 半导体行业观察,2020)。

四、单原子厚度沟道解决方案

2020年3月,Nature Communications接收一篇论文“A FinFET with One Atomic Layer Channel”,陈茂林博士、孙兴丹博士、刘航硕士为论文共同第一作者,韩拯教授、孙东明研究院、刘松教授、董宝娟讲师为共同通讯作者。

[pic 4-1: 单原子层沟道 FinFET]

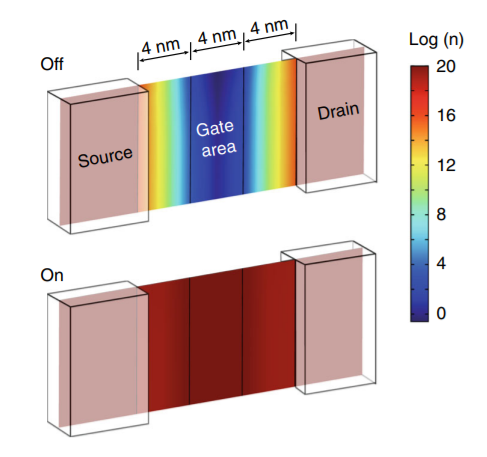

为了避免硅基平面场效应晶体管(Planar FET)因尺寸减小带来的短沟道效应等缺陷,鳍式晶体管(FinFET)将沟道做成鱼鳍状。由于微纳加工精度,FinFET沟道宽度最小约为3-5nm,集成电路尺寸逼近工艺和物理的极限,进一步缩小晶体管器件特征尺寸极具挑战。因此,中科院金属研究所韩拯教授及其团队设计了高度300nm的硅晶体台阶模板,以替代硅基Fin,将沟道宽度减小至0.6nm,沟道电流开关比达10^7。同时,获得最小间距为50nm单原子层沟道鳍阵列,为后摩尔时代提供新的解决方案(中科院行业动态,2020)。

首先,用于制作沟道的材料,如同胶片一样轻薄,只有0.6nm,即一个原子的宽度。沟道材料由二硫化钼、二硫化钨和碳纳米管组成,前两者经常被用于润滑剂中。关于碳纳米管,Carbon Nanotube (CNT),又名巴基管,是一种具有特殊结构的一维量子材料,主要由单层或多层的石墨片绕中心按一定角度卷曲而成的同轴中空无缝管状结构,其管壁大都是由六边形碳原子网络组成。CNT具有半导体或金属性质,由其结构决定导电性能。管中可以填充金属、氧化物等,以作纳米尺度的导线,用于芯片的沟道材料(知乎-十一维科研中心,2021; 中国粉体技术网,2014)。

[pic 4-2: Monolayer Channel Illustration

原文:陈茂林、孙兴丹、韩拯等,2020]

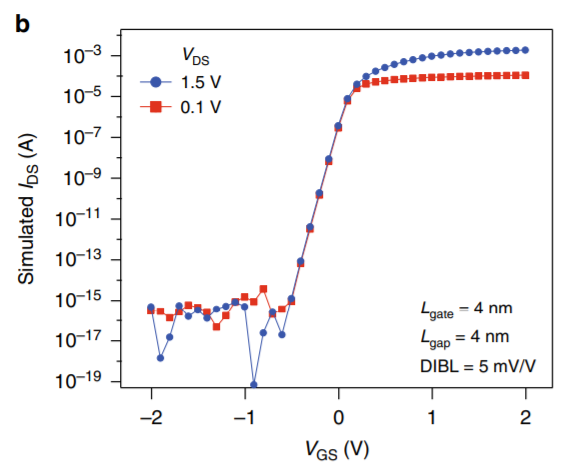

其次,制程4nm,可以有效避免短沟道效应。图4-3中的 On-Off Ratio,在4nm制程下几乎可控,使得Gate作用完善,有效节省能源。

[pic 4-3: On-Off Ratio of FinFET with Monolayer Channel,

Click For Source]

[pic 4-4: Monolayer FinFET I-V(GS)Curve,

Click For Source]

[pic 4-5: Similar Curve of JFET,

Click For Source ]

再者,单原子层FinFET转移特性,即I-V(GS)关系与结JFET类似。笔者认为,该数据用于确定在特定的Gate Source电压下,确定相应电流和Drain Source电压,使其符合欧姆定律抑或是其他范畴应用。

接着,为了进一步说明电流与Drain Source电压之间的关系。图4-7将输出曲线 I-V(DS) 与转移曲线 I-V(GS) 放在一起观察欧姆定律成立的可变电阻区,即途中的Linear Region。图4-6中的三大区域:可变电阻区、饱和区、击穿区的解释如下:

- 可变电阻区:该区域欧姆定律成立,电流随源漏极电压增加而增加,并且电流变化量与Gate Source电压(区别于源漏极电压)变化量的比值为常数,该比值称为“低频跨导”

- 饱和区:顾名思义,该区域电流恒定,不随源漏极电压改变而改变

- 击穿区:源漏极电压穿过饱和区继续增大,电流再次增大,电子器件可能遭到损坏(CSDN-作者,2020; 与非网,2016)

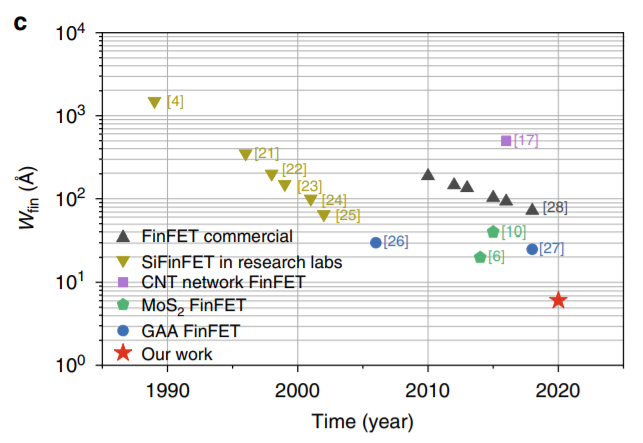

这篇论文除了解释制作工艺之外,还指出1990年至今,硅基FinFET和商用FinFET一直都是行业的宠儿,无论研发还是量产,始终采用该设计解决短沟道效应等由芯片尺寸减少带来的问题。这次0.6nm单原子层沟道及4nm制程的FinFET解决方案,在芯片尺寸上,可谓再一次达到里程碑级水平。让我们拭目以待,看技术推广应用,看是否能量产。

文章至此,无论是注重销售、关注热度的中芯国际,还是内功深厚、干劲十足的台积电,两家参与者通过他们不同的经营理念和行业理解,致力于这场芯片革命和产能转移。中国,甚至世界怎么迎接接下来的后摩尔时代,用什么样的配速发展,用什么样的产品一次又一次地撬动支点,都让人觉得兴奋不已。

[pic 4-7: Meaning of FinFET with Monolayer Channel]

请持续关注 ShoelessCai,致力于 “商业赋能行业”,打通信息屏障,加速信息要素流通。

延伸阅读

- Model S 精简模型

- 围观电动汽车:以Tesla为例

- 零基础学习芯片制造

- 如何理解“缺芯潮”?谁买不到芯片?

- 2021年车用芯片产能,能满足中美两国需求

参考文献

[1] ESMC-国际电子商情(2021),中芯国际人事大震荡:蒋尚义出走,梁孟松辞职,国际电子商情, 2021.

[2] 腾讯网-企鹅号1(2021), 梁孟松到底有多厉害?曾以一人之力,改变行业进程!, 腾讯网,2021.

[3] 腾讯网-企鹅号2(2021),中芯国际迎来高光时刻,3位大佬收入麾下,国产芯片未来可期,腾讯网,2021.

[4] 知乎问答(2020),如何评价梁孟松?,知乎,2020

[5] 知乎-智东西(2019),探秘台积电技术论坛!总裁魏哲家谈5nm进展,解读三大芯片技术,知乎,2019

[6] 网易科技(2021),台积电CEO:亚利桑那州5nm芯片厂已开工建设 斥资120亿美元,cnBeta,2021..

[7] 腾讯网-世界经理人商业(2021),避免产能不足!英特尔将派高管访台积电,腾讯网,2021

[8] 与非网(2017),魏哲家加刘德音抵得上一个张忠谋?比比就知道,维科网,2017.

[9] 知乎-张竞扬(2020),晶体管发展历史,知乎,2020

[10] 知乎-石大小生(2021),拯救摩尔定律:一文讲解GAA 芯片技术,知乎,2021

[11] 海西商界(2021),三星电子官宣3nm将实现量产:性能提升30%,功耗下降50%!,维科网,2021

[12] 搜狐号-风尘孤狼(2019),鳍式场效应晶体管基础知识解析,搜狐,2019

[13] 电子工程专辑(2020),台积电2nm工艺进展如何了?MBCFET架构获重大突破,电子工程专辑,2020.

[14] 半导体行业观察(2020),台媒:台积电2nm制程获重大突破,网易新闻,2020

[15] 中科院行业动态(2020),单原子层沟道的鳍式场效应晶体管,中科院半导体研究所,2020

[16] 知乎-科技美学(2021),工艺在进一步,三星展示3nm GAE MBCFET制造细节,知乎,2021

[17] Mao-Lin Chen, XIngdan Sun, Hang Liu, etc. (2020), A FinFET with One Atomic Layer Channel, Nature Communications, 2020

[18] 知乎-十一维科研中心(2021),碳纳米管的种类、特点及其应用,知乎,2021

[19] 中国粉体技术网(2014),碳纳米管的性能及应用领域,中国粉体技术网,2014

[20] 电子工程世界-匿名文章(2011),结型场效应管,电子工程世界,2011

[21] 知乎-温戈(2021),FinFET工艺技术详解,知乎,2021

[22] CSDN-作者(2020),深入浅出:结型场效应管原理应用——参考《模拟电子技术基础》清华大学华成英主,CSDN,2020

[23] hulx (2012),关于“结型场效应管JFET”的那些事讲,Hifi音响,2012

[24] 与非网-bobbi(2016),MOS管的这几种“击穿”,你搞清楚了吗?,与非网,2016